Inverter voltage stress

Transformer-less multilevel inverter (TMLI) with reduced device

Transformer-based inverters ensure isolation between the grid and the PV panel as a protective measure. Also, the transformer plays a crucial role in stepping up the input

Five-level transformerless inverter with reduced voltage

The employed semiconductors endure maximum voltage stress equivalent to the input voltage, while the switched capacitors (SCs) are rated at only half of the input voltage. This significantly

A Novel Single Source Bridgeless Nine-Level Switched-Capacitor

To address these issues further, a novel bridgeless common neutral switched capacitor multilevel inverter has been proposed in this article. The maximum voltage stress on

A High-Frequency Resonant Inverter Topology With Low-Voltage Stress

This paper presents a new switched-mode resonant inverter, which we term the inverter, that is well suited to operation at very high frequencies and to rapid on/off control. Features of this

A T-Type Switched-Capacitor Multilevel Inverter With Low Voltage Stress

This paper proposes a novel T-type multilevel inverter (MLI) based on the switched-capacitor technique. The proposed inverter not only achieves that the maximum

Grid-connected buck–boost inverter without shoot-through issue

Operating principle of the proposed inverter is illustrated. Voltage stress analysis, loss calculation, and filter design guidelines and example are given. Finally, simulation and

Five-level transformerless inverter with reduced voltage stress on

The employed semiconductors endure maximum voltage stress equivalent to the input voltage, while the switched capacitors (SCs) are rated at only half of the input voltage. This significantly

Antiresonance Phenomenon and Peak Voltage Stress Within

Abstract: The high-frequency behavior of the stator winding is synthesized herein using a multiconductor transmission line model to study the potential location of excessive voltage

Effects of Circuit-Level Stress on Inverter Performance and

Inverters are stressed with a ramped voltage stress (RVS) of various magnitudes to induce different degrees of gate oxide degradation. In addition, voltage transfer curves (VTCs) of

A new triple voltage gain seven level switched capacitor-based

The proposed inverter topology has minimum voltage stresses on the switches and balanced capacitor voltages. This paper briefs the operation of proposed topology, voltage stress

A new triple voltage gain seven level switched capacitor-based inverter

The proposed inverter topology has minimum voltage stresses on the switches and balanced capacitor voltages. This paper briefs the operation of proposed topology, voltage stress

A 13-level switched-capacitor-based multilevel inverter with

The maximum capacitor voltage stress in the 13-level switched capacitor inverter presented in 8 is one-third of the maximum output voltage. Although this structure has a high

Impact of the non-ideal condition in the analysis of high voltage

Switched impedance inverters are a category of power electronic converters that can be applied across various applications through the implementation of appropriate control

Motor Stator Insulation Stress Due to Multilevel Inverter Voltage

This paper investigates stress in medium-voltage motor insulation when the stator winding is excited by 3-, 5-, and 7-level multilevel inverter output waveforms. The effect of

Modeling and Verification of Electrical Stress in Inverter-Driven

This article develops a high-fidelity physics-based modeling approach to predict the voltage stress and current distributions in individual conductors of electric machine

Anti-resonance phenomenon and peak voltage stress within

The comprehensive modeling approach proclaims that the voltage distribution within the winding is a result of the anti-resonance phenomenon, which can be characterized by two oscillatory

asymmetrical multilevel inverter with minimum voltage stress and

This study proposes a new 17-level asymmetrical MLI with minimum voltage stress across the switches and fewer components. Fig. 1 provides a comprehensive overview of the

Effects of Circuit-Level Stress on Inverter Performance and

Abstract The effects of circuit-level stress on both inverter operation and MOSFET characteristics have been investigated. Individual MOSFETs, with gate oxide thicknesses of 3.2 nm and

Voltage Stress Modeling and Measurement for Random-Wound Windings

This paper studies voltage stress in complex machine windings under steep-fronted voltage excitations from inverter drives. Electrical stress in this paper includes voltage overshoots

Low-Voltage Stress Seven-Level Inverter Based on Symmetrical Capacitors

A step-up single-phase seven-level inverter is proposed in this article. The proposed multilevel inverter (MLI) uses one voltage source and two symmetrical capacitors.

Antiresonance Phenomenon and Peak Voltage Stress Within PWM Inverter

Abstract: The high-frequency behavior of the stator winding is synthesized herein using a multiconductor transmission line model to study the potential location of excessive voltage

Constant Boost Control of the Z-Source Inverter to Minimize

Pulsewidth-modulation (PWM) control for the Z-source inverter has to be modified to utilize the shoot-through states for voltage boost. Fig. 2 shows the traditional carrier-based PWM

More industry information

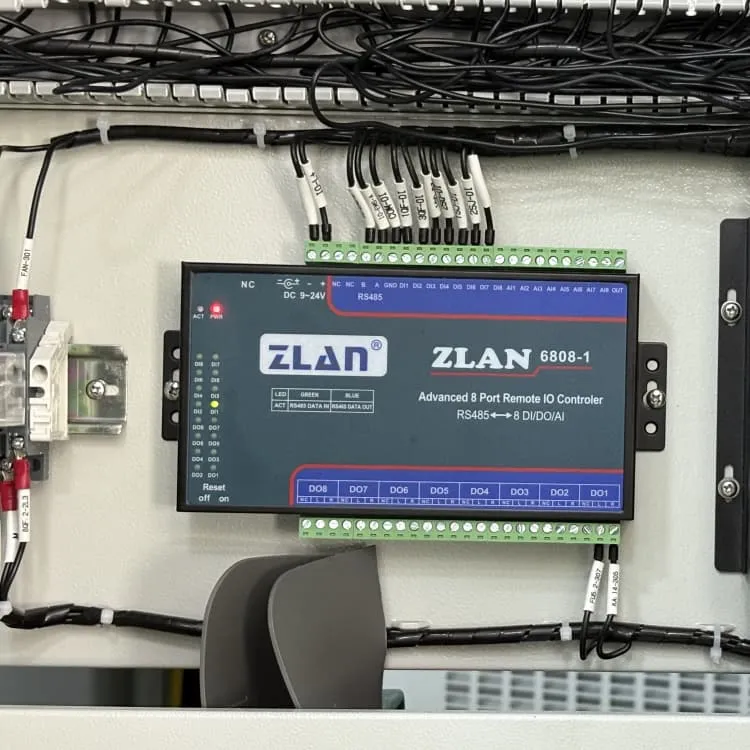

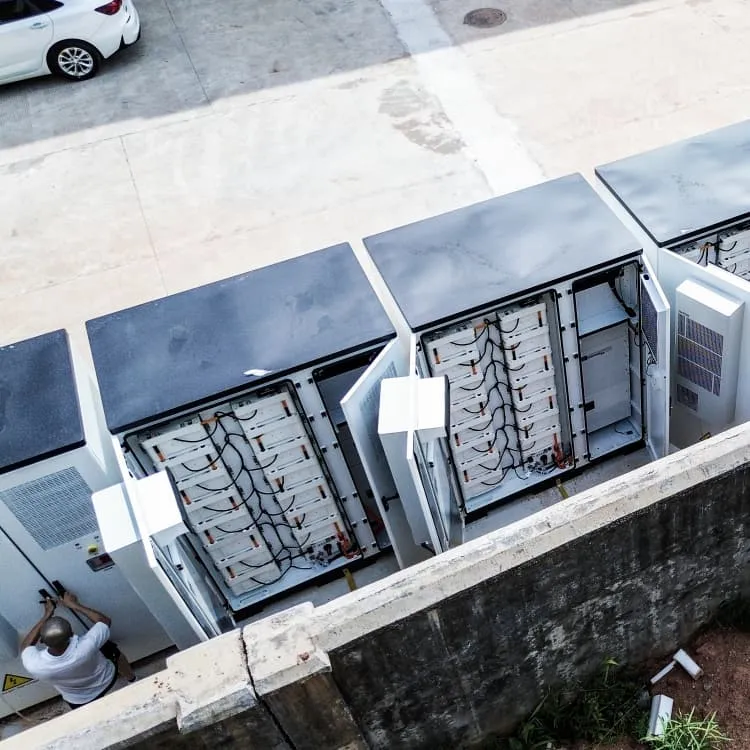

- What are the brands of smart energy storage cabinets in South Sudan

- Are flow batteries for communication base stations built on top of a slope

- Wholesale price of Russian power storage vehicle

- 6v 6w photovoltaic panel flexible board

- Photovoltaic inverters and containers

- Power supply side energy storage participates in peak load regulation

- Georgia micro solar power generation system

- Factory Battery Energy Storage

- Latvian lithium battery inverter

- Photovoltaic power generation high-power inverter

- Taipei Energy Storage Battery

- Guatemala Energy Storage Firefighting System

- Hydrogen energy storage cabinet

- How to achieve Internet access with communication base station batteries

- How to solve the problem of small grid-connected battery of communication base station inverter

- Solar Panel Manufacturer Direct Sales Integrated Photovoltaic Storage

- All-vanadium liquid flow energy storage batteries in Panama

- Malta Energy Storage Equipment Manufacturer Source Factory

- Korean outdoor battery cabinet BESS price

- Energy storage inverters balance the grid

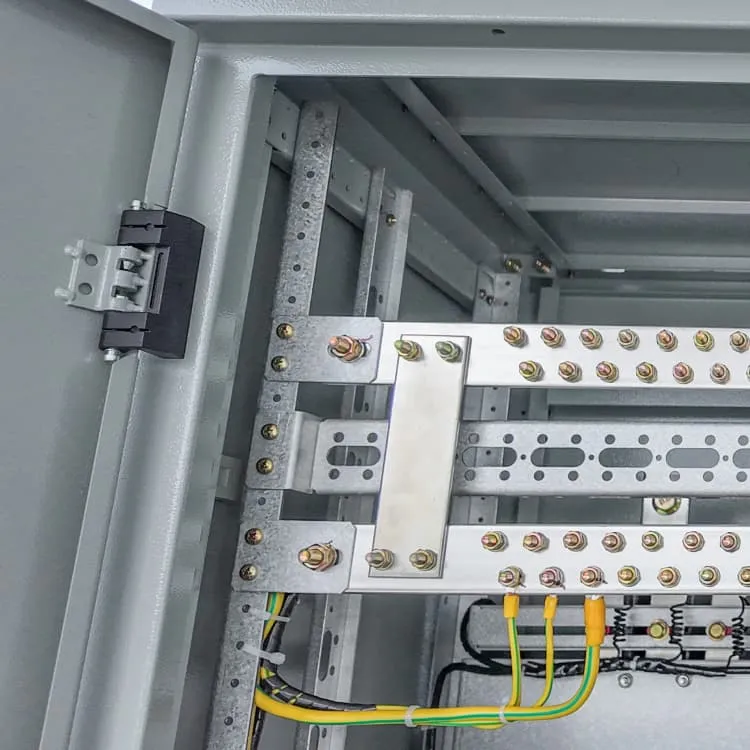

- Liquid-cooled energy storage container assembly process

- How much is the price of outdoor power supply in Liberia

- Can outdoor power supply replace household power supply in the long term

- Estimation of hybrid energy investment for communication base stations

- Portuguese villa roof photovoltaic panel manufacturer

- Zimbabwe solar panels photovoltaic panels

- Overview of battery costs for energy storage cabinets in Spain